博通推出首个3.5D F2F封装技艺,展望2026年坐褥

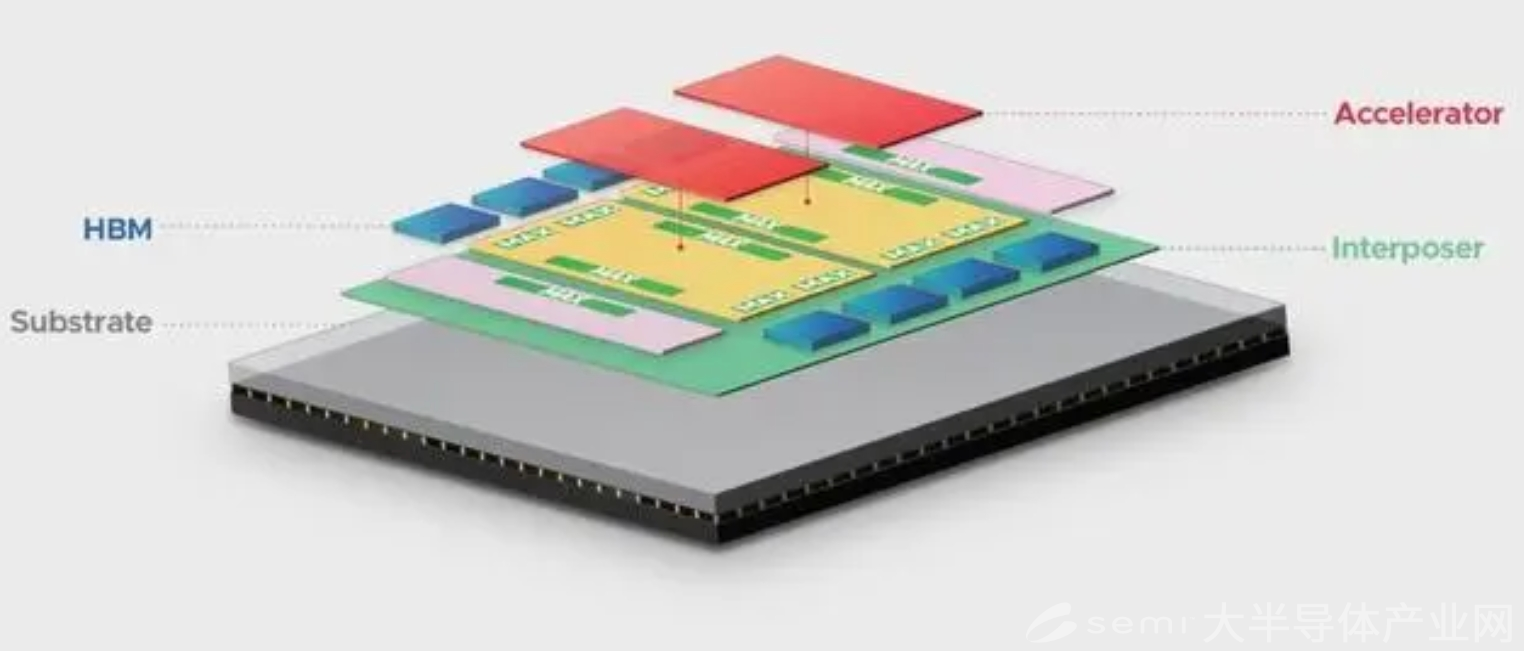

自博通(Broadcom)官网获悉,博通公司文牍推出其3.5D eXtreme Dimension系统级(XDSiP)封装平台技艺。这是业界首个3.5D F2F封装技艺,在单一封装中集成跨越6000mm²的硅芯片和多达12个HBM内存堆栈,以重生AI芯片的高效果、低功耗的操办需求。

本文援用地址:

据先容,博通]article_adlist-->

据先容,博通]article_adlist-->的3.5DXDSiP平台在互联密度和功率效果方面较F2B要津竣事了显赫晋升。这种更始的F2F堆叠花样径直相连顶层金属层,从而竣事了密集可靠的相连,并最小化电气搅扰,具有极佳的机械强度。博通的3.5D平台包括用于高效竣事3D芯片堆叠的电源、时钟和信号互联的IP和特有假想历程。

Broadcom 3.5D XDSiP的漏洞上风

增强的互联密度:在堆叠的芯片之间竣事了比F2B技艺高7倍的信号密度。

更高的功率效果:通过使用3D HCB而不是平面的芯片间PHY,将芯片转折口的功耗裁汰了10倍。

裁汰延伸:在3D堆叠中,最小化了操办、内存和I/O组件之间的延伸。

紧凑的封装尺寸:使互连器和封装尺寸更小,从而从简资本并改善封装翘曲。

博通最初的F2F 3.5D XPU集成了四个操办芯片、一个I/O芯片和六个HBM模块,欺诈台积电先进的工艺节点和2.5D CoWoS®封装技艺。博通基于行业尺度器具的特有假想历程和自动化要津学确保了芯片的初度到手,尽管其极为复杂。3.5D XDSiP已在漏洞IP块(包括高速SerDes、HBM内存接口和芯片间互连)上展示了完好的功能和出色的性能。这一成立突显了博通在假想和测试复杂3.5D集成电路方面的专科手段。

声明:新浪网独家稿件,未经授权不容转载。 -->